返回顶部

的发展取得了许多技术突破。图像传感器已发展成为支持许多应用的技术平台。它们在移动设备中的成功实施加速了市场需求,并建立了一个业务平台,以推动持续创新和性能改进,并将其扩展到监控、医疗和汽车行业。

在本文中,我们简要介绍了通用相机模块以及芯片堆叠架构和先进互连技术的关键技术要素。这项研究还将研究像素电子器件在确定芯片堆叠架构和互连技术选择方面的作用。它通过检查一些用于不同功能的 CMOS 图像传感器 (CIS) 示例来进行,例如可见光检测、用于低光检测的单光子雪崩(SPAD)、卷帘快门(rolling shutter)和全局快门(global shutter)以及深度感测和光检测以及测距(激光雷达)。

文章还介绍了不同芯片堆叠架构的性能属性。直接键合、后通孔硅通孔(Via-last TSV)和混合键合(HB)技术被认为是图像传感器芯片堆叠中较新且有利的芯片间互连技术。最先进的超高密度互连可制造性也得到了强调。

自2000年初以来,CMOS 图像传感器已被许多行业广泛采用。其多功能应用扩展到数码相机、移动设备、监控系统、机器人、医疗器械和自动驾驶汽车等许多行业。通过使用像素阵列中的光电二极管捕获图像并将信号实时转换为数字文件的能力可以实现高级数据管理和分析,从而实现其硬件与计算系统的兼容性。最近的进步使分析功能更接近像素阵列。机器学习(ML)、人工智能AI算法和图像传感器内的图像重建技术的实施已被广泛报道 。因此,图像传感器技术平台是许多应用的关键部分。

雷达和图像传感器的传感器融合、用于高级驾驶员辅助系统的光检测和测距 (LiDAR)、神经形态和高光谱成像、热成像和生物医学应用等先进应用正在不断发展。2018-2019年,图像传感器的市场规模已达到约200亿美元。预计从 2019 年到 2025 年,仅三维 (3D) 成像和传感市场的扩张将达到50亿至150亿美元,这几年的CGAR 为 20%。主要行业是消费移动产品和汽车行业。

技术平台和业务平台之间的协同效应已经显现。为了满足移动设备的外形尺寸限制,我们为具有巨大消费者需求的移动设备应用开发了先进的技术平台。移动设备建立的规模经济进一步鼓励先进的像素电子设计和使用芯片堆叠方法的像素并行处理在其他行业的应用。图像传感器将继续成为与业务平台协同的产品开发的强大技术平台。

像素电子产品的创新实现了多种先进功能。2000 年初,已有许多复杂图像传感器的设计被报道。只有当芯片堆叠和先进互连技术变得可制造时,这些创新的商业化才有可能实现。3D集成图像传感器的示范性设计始于1999年的四层堆叠,以及2004年多芯片堆叠架构中的多功能传感器。新实施的支持技术和特征尺寸的减小改变了拟议的 3D 集成。一些重大突破,如2009年的背照式(BSI) CIS、2012年的芯片堆叠、2015年的“pixel-DRAMlogic”三芯片堆叠、2016年的铜-铜混合键合(Cu-Cu hybrid bonding),这些技术都带来了最先进的技术平台。

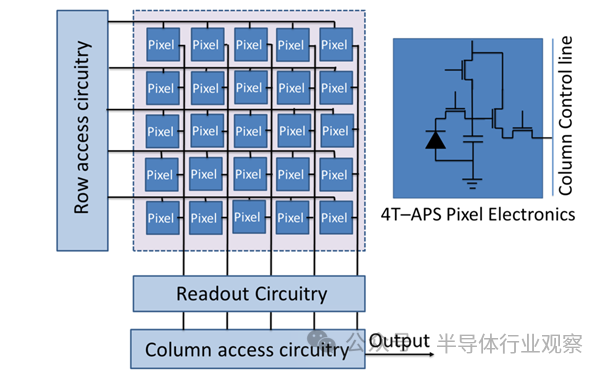

图像传感器是一种光电器件,通过光电二极管收集光源发出的光子,并将光电二极管产生的电流转换成数字信号。四晶体管有源光电二极管传感器 (4T-APS) 像素的典型像素电子器件由光电二极管和像素级电子器件组成,如图1右侧所示。图像由像素阵列形成,其原理图如图1中的方框区域所示。然后通过读出电路逐行评估像素阵列中的信号以进行进一步处理。行和列访问电路可以是用于扫描模式访问的开关阵列或用于随机像素访问的。

如今,图像传感器包含更多功能,用于读出功能后的信号处理和分析。通用操作电路可以包括用于高级应用的读出功能、模数转换、图像重马赛克处理或人工智能分析的电路。通过使用不同的感光材料,在不同的环境下,光检测的波长也可以从可见光到近红外或红外。对不同应用的巨大需求引发了这些领域的重大进展,不仅是研究和开发,而是将其商业化。

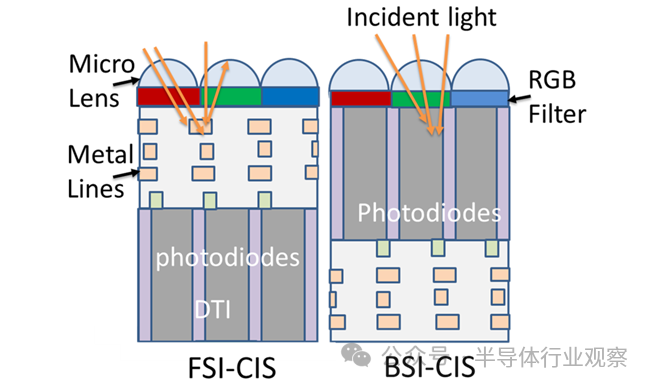

像素电子器件通常根据目标应用的光电二极管模式而变化。像素电子器件的范围可以从三晶体管3 T-APS 到 84 晶体管。像素电子器件和操作电路是影响芯片堆叠和互连方法选择的主要因素。基于不同照明方法的传感器也会影响芯片堆叠和互连架构的选择。由于金属互连线的遮光,前侧照明(FSI)CIS在像素尺寸低于1.4μm×1.4μm时大部分被BSI-CIS取代,如图2所示。

像素设计可能会有所不同,图2仅用于解释金属线屏蔽入射光的效果。例如,深沟槽隔离 (DTI:Deep trench isolation) 不需要 FSI-CIS 具有大像素尺寸。用于可见光检测的图像传感器通常称为 RGB(红、绿、蓝)图像传感器,具有简单的 3 T-APS 或 4 T-APS,当就位时还带有附加晶体管。通常需要红外 (IR) 滤光片(有时称为红外截止滤光片)来屏蔽超出可见光范围的波长,以减少穿透硅光电二极管薄层的近红外 (NIR) 光的干扰。微透镜层位于 RGB 滤光片的顶部,可增强投射到光电二极管区域的光。

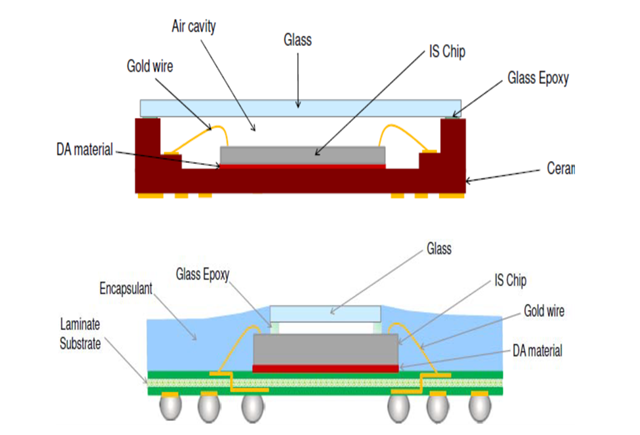

封装图像传感器的方法有很多种。两种常用的图像传感器封装是陶瓷无引线芯片载体和成像球栅阵列,原理图如图3所示。在新的多功能应用的推动下,新的图像传感器封装方法的开发仍在继续。探索了曲面图像传感器封装和超薄芯片级封装等先进应用。

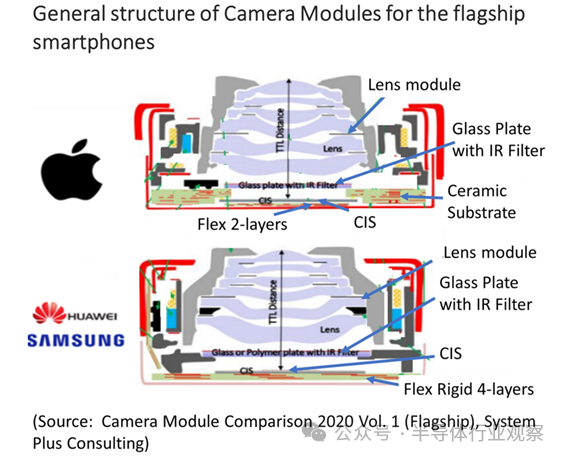

相机模块在顶部承载镜头模块,在底部承载图像传感器封装。System Plus Consulting分析的智能手机摄像头模块如图4所示。

顶部相机模块显示具有陶瓷基板的 CIS 封装,而底部模块则显示具有柔性刚性(flex-rigid)基板的 CIS 封装。精确安装图像传感器封装和相机镜头模块对于确保光投射对准至关重要。镜头模块的高度和图像传感器封装的尺寸是相互关联的并且被限制在相机模块内。随着的厚度越来越薄,相机模组的总高度受到限制。因此,相机模块的宽度和图像传感器的尺寸都被限制在狭小的物理空间中。

外形尺寸一直是将数码相机集成到智能手机和平板电脑中的关键因素。图像传感器的研究和开发旨在将相机模块安装在这些移动设备的狭小空间中,以实现多种应用。同时,分辨率的提高需要高像素密度、小像素尺寸以及高量子效率和高填充因子的光电二极管设计。本节中,我们总结了图像传感器的一些案例研究,并考虑了应用、所需的像素电子器件以及与 3D 集成相关的芯片堆叠和互连技术。当前工作的目的并不是关注图像传感器的性能。

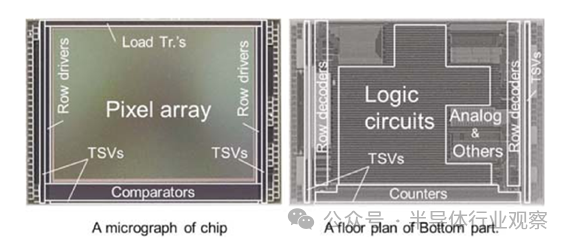

索尼公司于2012年8月20日发布了世界上第一个商业化的堆叠式图像传感器。图像传感器的性能在很多方面都得到了改进,例如更小的像素、更高的像素密度以及通过信号处理和图像重建来提高图像质量。Remosaic 算法通过分配具有长和短曝光时间的像素来提高质量,以帮助增加明亮和黑暗环境下成像的动态范围。复杂的操作电路导致芯片尺寸增加,这促使需要对芯片堆叠进行 3D 集成以保持较小的外形尺寸。像素阵列和逻辑处理电路被分成两个单独的芯片,如图5所示。堆叠式图像传感器不是基板上的单芯片图像传感器,而是将像素阵列芯片堆叠在逻辑电路芯片的顶部。

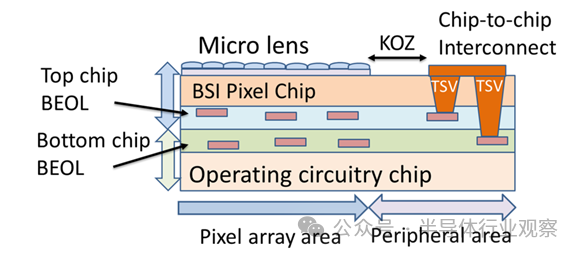

操作电路与像素阵列的电连接由用于芯片到芯片互连的外围后通孔TSV阵列形成,如图1和2所示。这些 TSV 在行驱动器到(driver-to-decoder)和列比较器(comparator)处连接到外围区域的计数器。TSV互连的数量与像素阵列的行和列访问的数量密切匹配,如图1所示。在这个 8 MP 图像传感器示例中,设计了数千个 TSV。芯片在电介质对电介质表面面对面粘合在一起,然后从 BSI 像素阵列芯片的背面形成最后通孔 TSV,落在两个芯片的金属焊盘上。重新分布层桥接最后通孔 TSV 以形成芯片到芯片互连。芯片堆叠和外围后通孔 TSV 的截面示意图如图6所示。像素尺寸为1.12μm×1.12μm。TSV 的直径 约为2.5μm,间距为6.3μm。像素芯片减薄至约8至9μm,硅基板厚度约 3至5μm。像素阵列芯片和处理芯片分别采用90纳米和65纳米技术加工。这使得尺寸仅为传统单芯片图像传感器的 70%,该设计的热管理经过测试并发现是足够的。

索尼通过从后通孔 TSV 转向外围芯片间互连的混合键合,进一步减小了芯片尺寸并简化了工艺。2016年的一份研究报告指出,研究人员正在研究在像素阵列下方以4μm间距放置混合键合 ,以进一步减小芯片尺寸。这一变化还消除了KOZ (Keep Out Zone) 和 TSV 蚀刻的附加处理设备而导致的器件设计规范。该图像传感器于 2016 年在iPhone6S 中推出。它是1.4μm像素尺寸、12MP BSI-CIS 图像传感器。混合键和间距分别为6μm和 14 μm。估计的混合键密度约为5000 bonds/mm2。

芯片堆叠可以提高性能并在两个单独的芯片中使用不同的处理技术。可以在不牺牲芯片尺寸的情况下将单独的优化和附加功能特征添加到操作电路芯片中。

三星采用芯片堆叠技术用于超过 16 MP 的 BSI-CIS 。其 108 MP BSI-CIS 已于 2019 年在智能手机中实现,当中像素阵列芯片使用65 nm 工艺,逻辑芯片使用28 nm 的技术。三星最近已转向采用 65 nm 技术的0.7μm像素,逻辑和信号处理器都采用 14 nm FinFET 工艺。采用 14 nm 工艺的 144 MP BSI-CIS 逻辑芯片比采用 28 nm 工艺的逻辑芯片功耗降低了 42%。在 65 nm–14 nm 处理技术中探索了 12 MP 双光电二极管 (2PD) BSI-CIS,与 65 nm–28 nm 技术处理的功耗相比,功耗降低了 29%。双光电二极管像素的每个光电二极管尺寸为0.7μm×1.4μm,导致像素尺寸为1.4μm×1.4μm,如图7所示。左右光电二极管信号之间的差异用于相移检测自动对焦数据,它们的总和用于输出图像数据。

通过使用 14 nm 技术,逻辑和图像处理的复杂性增加,从而允许相同的芯片尺寸具有更多功能。它还实现了 120 fps 的帧速率。这两种应用都使用堆叠芯片架构,直接键。

竞博电竞体育赛事平台 OA登录 友情链接 网站地图 企业电话:400-6655066

企业地址: 东莞市松山湖科技产业园区科技九路2号